����ժҪ������FPGA�ɾ���оƬ��Verilog HDL�Z(y��)�Ԍ�(sh��)�F(xi��n)�ˌ�(du��)ֱ��늙C(j��)PwM���������O(sh��)Ӌ(j��)����(du��)ֱ��늙C(j��)�ٶ��M(j��n)�п��ơ���B����Verilog HDL�Z(y��)�Ծ��̌�(sh��)�F(xi��n)ֱ��늙C(j��)PwM��������PwM�a(ch��n)��ģ�K������ͨ��ģ�K���D(zhu��n)���{(di��o)��(ji��)ģ�K�ȹ��ܣ�ԓϵ�y(t��ng)�o(w��)����D��A�D(zhu��n)�Q����ģ�M���^�����Y(ji��)��(g��u)��(ji��n)�Σ����ƾ��ȸߣ��ЏV���đ�(y��ng)��ǰ����ͬ�r(sh��)������ϵ�y(t��ng)��������λ�C(j��)���ƹ��ܣ��ɷ��㌦(du��)늙C(j��)�M(j��n)���h(yu��n)�̿��ơ�

���������P(gu��n)�I�~��FPGA������ͨ�ţ�PwM��ֱ��늙C(j��)����(sh��)�(y��n)�� �Ԃ��y(t��ng)�ķ����a(ch��n)��PwM��̖(h��o)�·���^��(f��)�s����(sh��)��PWM����ֻ��FPGA�еă�(n��i)���YԴ�Ϳ��Ԍ�(sh��)�F(xi��n)��

�������Ľ�B��һ�N�Æ�Ƭ��Ҏ(gu��)ģFPGA��(sh��)�F(xi��n)�İl(f��)����ֱ��늙C(j��)�����������Юa(ch��n)����PwM�������}�_���Č�(du��)�Q��PwM���ں����^(q��)�r(sh��)�g�ɾ��̵����c(di��n)�������܃�(y��u)�����`���ԺͿɿ��Ըߣ�ͬ�r(sh��)�������˴���ͨ�Ž��գ����������λ�C(j��)���ƹ��ܡ�

�����Ô�(sh��)�ֱ��^������ģ�M���^������(sh��)�ֱ��^����һ�˽��O(sh��)��ֵӋ(j��)��(sh��)����ݔ������һ�˽Ӿ����f��Ӌ(j��)��(sh��)��ݔ������(d��ng)����Ӌ(j��)��(sh��)��Ӌ(j��)��(sh��)ֵС���O(sh��)��ֵ�r(sh��)ݔ�����ƽ�������O(sh��)��ֵ�r(sh��)ݔ�����ƽ���cģ�M������ȣ�ʡȥ����ӵ�D��A�D(zhu��n)�Q����ģ�M���^����F(xi��n)PcA�ⲿ�B�����٣��·���Ӻ�(ji��n)�Ρ�����ͨ�^(gu��)������(sh��)��(j��)���I������ϵ�y(t��ng)�{(di��o)���}����(sh��)����(sh��)�ֱ��^�����O(sh��)��ֵ���Ķ���(sh��)�F(xi��n)��(du��)늙C(j��)�D(zhu��n)�١�����(d��ng)�ȅ���(sh��)���`����ơ�

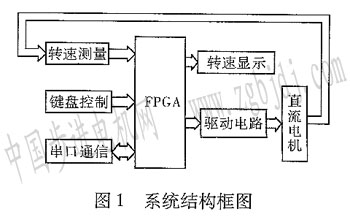

����ϵ�y(t��ng)���w�O(sh��)Ӌ(j��)ϵ�y(t��ng)�����w��D��Dl��ʾ��ԓϵ�y(t��ng)��оƬ����ƺ��ģ�ͨ�^(gu��)���I����λ�C(j��)�O(sh��)��늙C(j��)�ٶȺ�PwMռ�ձȣ���FPGA��I��O�ڿ���ֱ��늙C(j��)�(q��)��(d��ng)оƬ�(q��)��(d��ng)ֱ��늙C(j��)���D(zhu��n)��(d��ng)���D(zhu��n)�ٵĜy(c��)���ɴa�P��ɣ��ٶ��@ʾ��(sh��)�a�܁�(l��i)��(sh��)�F(xi��n)����ϵ�y(t��ng)�ǻ��ڌ�(sh��)�F(xi��n)늙C(j��)�ĺ����{(di��o)��(ji��)���M(j��n)���O(sh��)Ӌ(j��)�ġ�

����ϵ�y(t��ng)�����ׂ�(g��)ģ�K���D(zhu��n)���{(di��o)��(ji��)ģ�K���}���{(di��o)��(PwM)ģ�K���ٶșz�y(c��)ģ�K������ͨ��ģ�K��

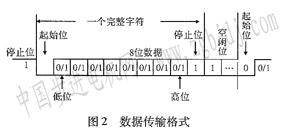

����1��1����ͨ��ģ�K���O(sh��)Ӌ(j��)�в�ȡ��������ͨ�š���һ��(g��)�ַ����λ���ͣ���ҪcPu�c��λ�C(j��)֮�g���ȱ�횼s���ַ���ʽ�Ͳ����ʡ��O(sh��)Ӌ(j��)���ù̶����ַ���ݔ��ʽ��һλ��ʼλ��8λ��(sh��)��(j��)��һλֹͣλ����D2��ʾ��

������������ǵ�λ��ǰ����λ�ں������͡�

������4��������������ղɘӕr(sh��)犣����ѵ�8��(g��)�ɘ�ֵ������Ք�(sh��)��(j��)������FPGA��(sh��)�F(xi��n)�Į�������ͨ���·�в���FIFO�M(j��n)�о��棬���ڄ��֞����ģ�K���l(f��)��ģ�K�ͽӿ�ģ�K����(g��)����ģ�K�����н���ģ�K��(sh��)�F(xi��n)�b�y(c��)��(sh��)��(j��)�Ľ��ա����棬�l(f��)��ģ�K��(sh��)�F(xi��n)�b��?c��i)?sh��)��(j��)�ľ��桢�l(f��)�ͣ��ӿ�ģ�K�t��(sh��)�F(xi��n)���ⲿ���B�ӡ��l(f��)��ģ�KҪ��(sh��)�F(xi��n)��(du��)�b��?c��i)?sh��)��(j��)���棬ͬ�r(sh��)�����O(sh��)Ӌ(j��)�Į�������ͨ���ַ���ʽ����(sh��)��(j��)���аl(f��)�͡��l(f��)��ģ�K������λ�Ĵ�������(sh��)�F(xi��n)�b�y(c��)��(sh��)��(j��)Ӌ(j��)��(sh��)��Ӌ(j��)��(sh��)���Ͱl(f��)�͠�B(t��i)�C(j��)�·�ȡ�

������D3��ʾ��F(xi��n)PGAģ�K���Տ�RSһ485�l(f��)���^(gu��)��(l��i)�Ĵ��Д�(sh��)��(j��)��25λ��һ��(g��)�ַ���ԓģ�K�քe��(sh��)�F(xi��n)��ȡ��λ��(sh��)��(j��)�ʹ��Д�(sh��)��(j��)�l(f��)�͵Ĺ��ܡ���(d��ng)�B�m(x��)ݔ��16��(g��)l����һ��(g��)din��O�r(sh��)���_ʼ��ȡ�����8λ��Ч�Ĕ�(sh��)��(j��)00101010��Ȼ�������ʼλ1��ֹͣλO�������У������ʿ��Ը���(j��)��Ҫͨ�^(gu��)���l�����M(j��n)�иĄ�(d��ng)��

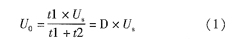

����1����2�D(zhu��n)���{(di��o)��(ji��)ģ�Kֱ��늄�(d��ng)�C(j��)�D(zhu��n)�ٵĿ��Ʒ����ɷ֞�������(l��)�ſ��Ʒ��c늘�늉����Ʒ�����ϵ�y(t��ng)����늘�늉����Ʒ�����ͨ�^(gu��)�{(di��o)��(ji��)PwM�|�l(f��)��̖(h��o)��ռ�ձȁ�(l��i)��׃�ŷ�늙C(j��)��ƽ��ݔ��늉����Ķ���(sh��)�F(xi��n)�{(di��o)�ٵ�Ŀ�ġ�늄�(d��ng)�C(j��)��늘��@�M�ɶ˵�늉�ƽ��ֵ�飺

����ʽ�У�D��ռ�ձȣ�Us�Դ늉���D��׃��������[O��1]����ʽ(1)��֪����(d��ng)�Դ늉�us��׃����r�£�늘Ѓɶ�늉���ƽ��ֵUoȡ�Q��ռ�ձȵĴ�С����׃DֵҲ��׃��늘Ѓɶ�늉���ƽ��ֵ���Ķ��_(d��)������늄�(d��ng)�C(j��)�D(zhu��n)�ٵ�Ŀ�ģ�����(sh��)�F(xi��n)PwM���ơ�

����1��3 PwM�a(ch��n)��ģ�K�}�_�{(di��o)��PwM ԭ����FPGA�еĻ���(zh��n)Ӌ(j��)��(sh��)�����Á�(l��i)�a(ch��n)�����ģ�M�·�е����Dz�����(zh��n)����һ��(g��)��СӋ(j��)��(sh��)ֵ��O��****Ӌ(j��)��(sh��)ֵ�����ڼĴ����б���Ĕ�(sh��)ֵ��Ӌ(j��)��(sh��)������׃���Ŀ���Ӌ(j��)��(sh��)����

����ͬ�r(sh��)����(zh��n)Ӌ(j��)��(sh��)����Ԫ�a(ch��n)��һ��(g��)������̖(h��o)DIR���������ⲿ�Д�Դ(߅���|�l(f��)��ʽ)����PwM�_�P(gu��n)���ڵ���ʼ�c(di��n)�a(ch��n)���Дࡣ

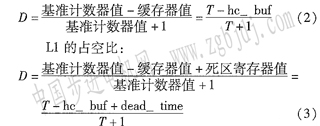

����ܛ���O(sh��)Ӌ(j��)�^��(ji��n)�Σ��ڳ�ʼ���A���O(sh��)�ú����ڼĴ��������^(q��)�Ĵ������Ժ�ֻ����PWM�Д����(w��)�����Ќ�Ӌ(j��)��õ��}����(sh��)��(j��)�͵��}���Ĵ�����Ȼ���˳��Д����(w��)���ȴ����������|�l(f��)�}�_�������}���Ĵ����Ĕ�(sh��)��(j��)�i�浽���_�Ĵ����С�����һ��(g��)������ݔ������(y��ng)���}�_��ͬ�r(sh��)�Д౻�|�l(f��)�����_ʼ����һ��(g��)PwM�Д����(w��)���D4��PwM�a(ch��n)��ԭ��D������H1��ռ�ձȣ�

������ҊHl��L1��ռ�ձ�D�ɻ���(zh��n)Ӌ(j��)��(sh��)��ֵT�;�����ֵhe��buf�����^(q��)�Ĵ���ֵ��ͬ�Q����ͨ�^(gu��)������(sh��)��(j��)���߰��I�{(di��o)��(ji��)�քe�������ڣ��}�������^(q��)�Ĵ�����ֵ��(l��i)�{(di��o)��(ji��)ռ�ձȣ�����늙C(j��)���١��p�١�

�����D5��PwM������Y(ji��)��������D5��ʾT�͡�buf��ֵ�����_��׃�����ڞ�50��ռ�ձȞ飥��PwM����ݔ�������^(q��)�r(sh��)�g3Ҳ�����_�ؼ��룬�a(ch��n)����4·�������^(q��)��PwM���Ρ�

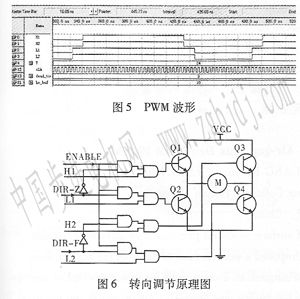

��1����4�D(zhu��n)���{(di��o)��(ji��)ģ�K�D6���D(zhu��n)���{(di��o)��(ji��)ԭ��D���Ѓɂ�(g��)������̖(h��o)��һ��(g��)ʹ����̖(h��o)�����DIR��z��̖(h��o)��0��DIR��F��̖(h��o)��l������ʹ����̖(h��o)��1����ô���O��Q1��Q4��(d��o)ͨ�����������������(j��ng)늙C(j��)��늙C(j��)���D(zhu��n)�������z��̖(h��o)׃?y��u)?����DIR��F��̖(h��o)׃?y��u)�O����ô��Q3����(d��o)ͨ������t�������^(gu��)늙C(j��)��늙C(j��)���D(zhu��n)��

��������Hl��L1��H2��12����PwMģ�K�a(ch��n)����һ��ռ�ձȵ�PWM�����Á�(l��i)����늙C(j��)�D(zhu��n)�١�

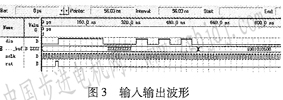

������(sh��)�(y��n)�D7���Ô�(sh��)��ʾ�����ɘӡ�����FPcA��ֱ��늄�(d��ng)�C(j��)����ϵ�y(t��ng)ռ�ձȞ�74 6����PwM���Ρ����l���S늙C(j��)�D(zhu��n)��׃������׃FPGA�����е�T�͡�buf���ɸ�׃PwM���ε�ռ�ձȡ�

����3 �Y(ji��)�Z(y��)ֱ��늙C(j��)

���ھ����ٶȿ������ף������Ƅ�(d��ng)�������ã����ڌ�������(n��i)F���{(di��o)�ٵ����c(di��n)����ұ�𡢙C(j��)е���졢�p���ȹ��I(y��)���T�еõ��V����(y��ng)�á�

������������B��ֱ��늙C(j��)PWM���������Ľo�������O(sh��)Ӌ(j��)FPGA�}���{(di��o)�ƿ��Ʒ�����Ӌ(j��)��C(j��)����ĽY(ji��)��������ԓ�·����Ч�خa(ch��n)��PwM������̖(h��o)����늙C(j��)���D(zhu��n)�٣����ƾ�����FPGA�еĔ�(sh��)�ֱ��^���Q����Ӳ���·���(ji��n)�Σ�������a�������ס���FPGA��I��0�ڮa(ch��n)��PwM������̖(h��o)��һƬF(xi��n)PGA����ͬ�r(sh��)ݔ����·PwM��̖(h��o)������ͨ���ԣ��O(sh��)Ӌ(j��)ͬ�r(sh��)������(sh��)�F(xi��n)��������ͨ�ŵĹ��ܣ����Ԍ�(sh��)�F(xi��n)��(du��)��(sh��)��(j��)�Ľ��պͰl(f��)�ͣ��������ڽ��Ք�(sh��)��(j��)�r(sh��)��(du��)��У�(y��n)λ��ֹͣλ�M(j��n)���Д࣬�ڰl(f��)�͔�(sh��)��(j��)�r(sh��)�����γ�������һ����(sh��)��(j��)��ʽ����ԓ��������ͨ�Žӿ��O(sh��)Ӌ(j��)��(sh��)�F(xi��n)�Ĕ�(sh��)��(j��)�ɼ��c̎��ϵ�y(t��ng)�У����Գɹ��،�(sh��)�F(xi��n)���h(yu��n)�˵���λ�C(j��)�M(j��n)�Ю�������ͨ�ţ������M(j��n)���h(yu��n)�̿��ơ�

����

|